So, I’ve gotten me a few books on processor design, from the ground up.

One is a first edition of ‘Digital Computer Electronics’ by Albert Paul Malvino and Jerald A. Brown from 1977. The second one is ‘The Elements of Computing Systems: Building a Modern Computer from First Principles’ by Noam Nisan and Shimon Schocken from 2005.

The first is, as expected diving into actual hardware with the full gamut of digital circuits and a set of three Simple As Possible computers, while the second goes a more software simulation route for developing a simple Hack Computer, but goes deeper into software, like Assembler and even Programming languages for the computer.

Suffice to say, reading, or even just looking through the books gave me a few insights about my ALU design.

ALU Modifications

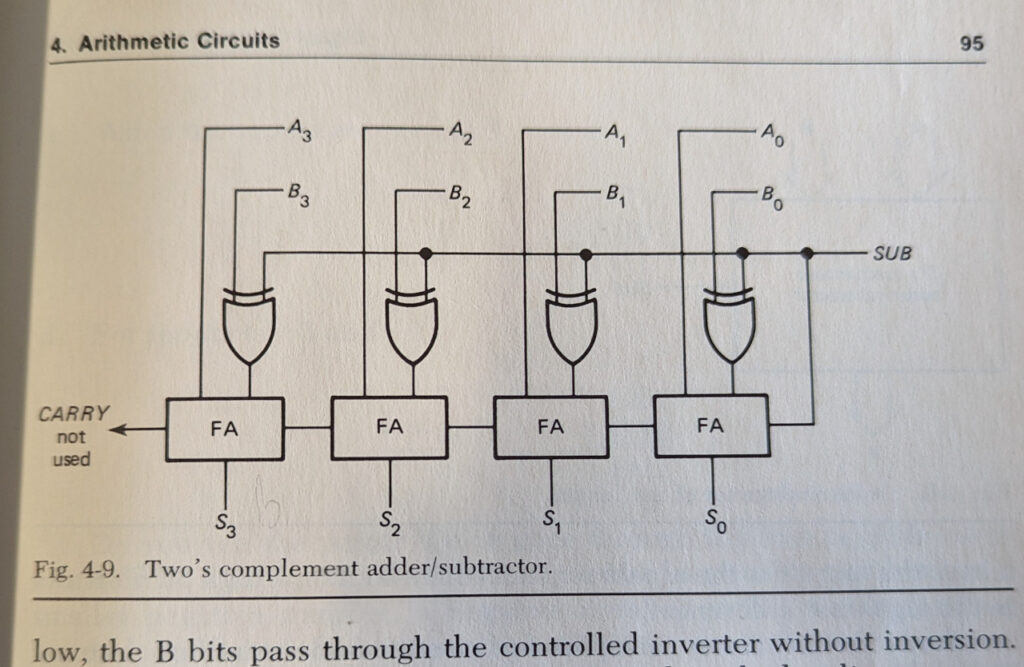

For one, there is a simplification, concerning the substration, and replacing the multiplexer by with four XOR gates.

Since this removed the need to have the $ \overline{B} $, I also decided to remove $ Ā $ as well, as four NOT gates are hardly that much added complexity. And it certainly gets rid of eight input signals.

So, for the time being, this is the current ALU design.

Yes, I do notice that the Sub input is not connected to the Carry input, as its a bit sliced ALU, so Ci can take the Co from a previous ALU in the chain. So, setting the Ci for a substraction will need to be done by the control logic of the ALU.

Status Flags

C: Carry Flag

The Carry Flag should be pretty self explanatory. It’s simply the carry bit that comes out at the end of a ln ALU operation.

QC, HC, TC: Bit Sliced Carry Flags

The Quarter Carry, Half Carry and Three Quarter Carry are simply the three carry bits that are exchanged between the 4 bit bit sliced ALUs.

I’m not really sure how useful these flags are, but I have access to them.

Z: Zero Flag

This flag is set if the result of the last ALU operation is zero, or, in a branch/compare operation, a register is zero

EQ: Equal Flag

This flag is set if the two operators of the last ALU operation are equal, or, in a branch/compare operation, the Te’o selected registers are equal.

N: Negative Flag

This flag is set if the result of the last ALU operation is negative. I think I will use mostly signed integers internally, so it will be set if the MSB of a 16 bit value is set, aka 2nd complement. However, for comparison operations on unsigned integers, it will be set to the inverse of the carry flag.

O: Overflow Flag

This flag is set when the result of an arithmetic operation would be outside the bounds of a signed value. E.g. 32668 + 400 = 33068, which would be outside the bounds of -32768 to +32767.

IE: Interrupt Enable Flag

This flag tells the CPU to Enable/Disable the interrupt handling. Used e.g. in interrupt handler routines.

You do not want to interrupt your interrupt while handling the previous interrupt.

I0-I2: Interrupt Flag

These three flags tell the CPU the current/next interrupt handler, for use when IE is disabled. So the CPU can handle the next interrupt after completing the previous.

When I0-I2 are set to 0, no interrupt is called. Can be set by software to call an interrupt handler.

Might be combined with a short FIFO memory for multiple interrupts.

Tentative Flag Register Layout

| LSB | MSB | ||||||||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| Z | N.A. | C | QC | HC | TC | N.A. | EQ | N | O | N.A. | N.A. | IE | I0 | I1 | I2 |

So, if there are any more Flags I might need, I can add four more. Though it does not seem likely.